# Failure Modes, Effects and Diagnostic Analysis

Project:

Surge protective devices

PLUGTRAB PT

Customer:

PHOENIX CONTACT GmbH & Co. KG

Blomberg

Germany

Contract No.: Phoenix Contact 14/09-007

Report No.: Phoenix Contact 14/09-007 R020

Version V2, Revision R1, March 2016

Stephan Aschenbrenner

The document was prepared using best effort. The authors make no warranty of any kind and shall not be liable in any event for incidental or consequential damages in connection with the application of the document.

© All rights reserved.

## **Management summary**

This report summarizes the results of the hardware assessment carried out on the surge protective devices PLUGTRAB PT in the versions listed in the drawings referenced in section 2.5.1. Table 1 gives an overview of the different configurations that belong to the considered surge protective devices PLUGTRAB PT.

The hardware assessment consists of a Failure Modes, Effects and Diagnostics Analysis (FMEDA). A FMEDA is one of the steps taken to achieve functional safety assessment of a device per IEC 61508. From the FMEDA, failure rates are determined and consequently the Safe Failure Fraction (SFF) is calculated for the device. For full assessment purposes all requirements of IEC 61508 must be considered.

Only the described configurations were analyzed. All other possible variants or electronics are not covered by this report.

Surge protective devices are not considered to be elements according to IEC 61508-4 section 3.4.5 as they are not performing one or more element safety functions. Therefore, there is no need to calculate a SFF (Safe Failure Fraction). Only the interference on a safety functions needs to be considered. This interference is expressed in a contribution to the overall PFD<sub>AVG</sub> / PFH.

The failure rates used in this analysis are from the *exida* Electrical Component Reliability Handbook ([N2]) for Profile 1 <sup>1</sup>.

**Table 1: Configuration overview**

| PT 2x2DC/AC | Protective plug PT with protective circuit for two 2-core floating signal circuits; nominal voltages: 5 VDC, 12 VDC, 24 VDC, 12 VAC and 24 VAC; HART compatible.  Available with base element directly connected to the mounting or |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | connected via gas discharge tube with the mounting.                                                                                                                                                                                 |

| PT 1x2DC/AC | Protective plug PT with protective circuit for one 2-core floating signal circuits; nominal voltages: 5 VDC, 12 VDC, 24 VDC, 12 VAC and 24 VAC; HART compatible.                                                                    |

|             | Available with base element directly connected to the mounting or connected via gas discharge tube with the mounting.                                                                                                               |

| PT 4DC/AC   | Protective plug PT with protective circuit for a 4-core floating signal circuit; nominal voltages: 5 VDC, 12 VDC, 24 VDC and 24 VAC.                                                                                                |

|             | Available with base element directly connected to the mounting or connected via gas discharge tube with the mounting.                                                                                                               |

| PT 3DC      | Protective plug PT with protective circuit for two signal wires with common mode voltage coarse and fine protection to ground and additional fine protection between the two signal wires; nominal voltage: 24 VDC.                 |

|             | Available with base element directly connected to the mounting.                                                                                                                                                                     |

| PT 4-F      | Protective plug PT with coarse protection for four signal lines grounded on one side.                                                                                                                                               |

|             | Available with base element directly connected to the mounting.                                                                                                                                                                     |

Phoenix Contact 14-09-007 R020.docx; March 30, 2016 Page 2 of 46

<sup>&</sup>lt;sup>1</sup> See Appendix 3 for further details on the selected profile.

| PT 5-HFDC              | Surge voltage protection device for normal mode voltage coarse and fine protection for four floating signal wires and ground in IT, common mode voltage coarse protection to ground/earth; nominal voltages: 5 VDC, 12 VDC and 24 VDC. Available with base element directly connected to the mounting or connected via gas discharge tube with the mounting. |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PT 3-HFDC /<br>PT 3-PB | Surge voltage protection device for normal mode voltage coarse and fine protection for two floating signal wires and ground in IT, common mode voltage coarse protection to ground/earth; nominal voltages: 5 VDC and 12 VDC. Available with base element directly connected to the mounting or connected via gas discharge tube with the mounting.          |

| PT 2-TELE              | Surge voltage protection device, consisting of plug and base element, for protecting a double wire from analog and digital telecommunications interfaces (VDSL up to 50 Mbps). Available with base element directly connected to the mounting.                                                                                                               |

The following tables show how the above stated requirements are fulfilled.

Table 2: Summary for PT 2x2-...DC/AC-ST and BE - Failure rates <sup>2</sup>

|                                                       | exida Profile 1         |                         |

|-------------------------------------------------------|-------------------------|-------------------------|

|                                                       | Analysis 1 <sup>3</sup> | Analysis 2 <sup>4</sup> |

| Failure category                                      | Failure rates (in FIT)  | Failure rates (in FIT)  |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                       | 0                       |

| Fail Safe Undetected ( <sub>SU</sub> )                | 2.7                     | 2.7                     |

| Fail Dangerous Detected ( DD)                         | 0                       | 3.9                     |

| Fail Dangerous Undetected ( DU)                       | 5.8                     | 1.9                     |

|                                                       |                         |                         |

| No effect                                             | 26                      | 26                      |

| No part                                               | 0                       | 0                       |

|                                                       |                         |                         |

| Total failure rate (interfering with safety function) | 8.5 FIT                 | 8.5 FIT                 |

| МТВБ                                                  | 3328 years              | 3328 years              |

© exida.com GmbH

Stephan Aschenbrenner

Phoenix Contact 14-09-007 R020.docx; March 30, 2016

<sup>&</sup>lt;sup>2</sup> It is assumed that complete practical fault insertion tests can demonstrate the correctness of the failure effects assumed during the FMEDA.

<sup>&</sup>lt;sup>3</sup> Analysis 1 represents a worst-case analysis.

<sup>&</sup>lt;sup>4</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

Table 3: Summary for PT 2x2-...DC/AC-ST and BE+F - Failure rates 5

|                                                       | <i>exida</i> F          | exida Profile 1         |  |

|-------------------------------------------------------|-------------------------|-------------------------|--|

|                                                       | Analysis 1 <sup>6</sup> | Analysis 2 <sup>7</sup> |  |

| Failure category                                      | Failure rates (in FIT)  | Failure rates (in FIT)  |  |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                       | 0                       |  |

| Fail Safe Undetected ( <sub>SU</sub> )                | 2.7                     | 2.7                     |  |

| Fail Dangerous Detected ( DD)                         | 0                       | 3.9                     |  |

| Fail Dangerous Undetected ( DU)                       | 5.8                     | 1.9                     |  |

|                                                       |                         |                         |  |

| No effect                                             | 46                      | 46                      |  |

| No part                                               | 0                       | 0                       |  |

|                                                       |                         |                         |  |

| Total failure rate (interfering with safety function) | 8.5 FIT                 | 8.5 FIT                 |  |

|                                                       | 1                       | Τ                       |  |

| MTBF                                                  | 2102 years              | 2102 years              |  |

Stephan Aschenbrenner

Phoenix Contact 14-09-007 R020.docx; March 30, 2016

<sup>&</sup>lt;sup>5</sup> It is assumed that complete practical fault insertion tests can demonstrate the correctness of the failure effects assumed during the FMEDA.

<sup>&</sup>lt;sup>6</sup> Analysis 1 represents a worst-case analysis.

<sup>&</sup>lt;sup>7</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

Table 4: Summary for PT 1x2-...DC/AC-ST and BE - Failure rates 8

|                                                       | exida Profile 1         |                          |

|-------------------------------------------------------|-------------------------|--------------------------|

|                                                       | Analysis 1 <sup>9</sup> | Analysis 2 <sup>10</sup> |

| Failure category                                      | Failure rates (in FIT)  | Failure rates (in FIT)   |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                       | 0                        |

| Fail Safe Undetected ( <sub>SU</sub> )                | 2.7                     | 2.7                      |

| Fail Dangerous Detected ( DD)                         | 0                       | 3.9                      |

| Fail Dangerous Undetected ( DU)                       | 5.8                     | 1.9                      |

|                                                       | _                       |                          |

| No effect                                             | 26                      | 26                       |

| No part                                               | 0                       | 0                        |

|                                                       |                         |                          |

| Total failure rate (interfering with safety function) | 8.5 FIT                 | 8.5 FIT                  |

|                                                       | 1                       | ,                        |

| MTBF                                                  | 3328 years              | 3328 years               |

$<sup>^{8}</sup>$  It is assumed that complete practical fault insertion tests can demonstrate the correctness of the failure effects assumed during the FMEDA.

<sup>&</sup>lt;sup>9</sup> Analysis 1 represents a worst-case analysis.

<sup>&</sup>lt;sup>10</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

Table 5: Summary for PT 1x2-...DC/AC-ST and BE+F – Failure rates <sup>11</sup>

|                                                       | exida Profile 1          |                          |

|-------------------------------------------------------|--------------------------|--------------------------|

|                                                       | Exiua F                  | Totile 1                 |

|                                                       | Analysis 1 <sup>12</sup> | Analysis 2 <sup>13</sup> |

| Failure category                                      | Failure rates (in FIT)   | Failure rates (in FIT)   |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                        | 0                        |

| Fail Safe Undetected ( su)                            | 2.7                      | 2.7                      |

| Fail Dangerous Detected ( DD)                         | 0                        | 3.9                      |

| Fail Dangerous Undetected ( DU)                       | 5.8                      | 1.9                      |

|                                                       |                          |                          |

| No effect                                             | 46                       | 46                       |

| No part                                               | 0                        | 0                        |

|                                                       |                          |                          |

| Total failure rate (interfering with safety function) | 8.5 FIT                  | 8.5 FIT                  |

|                                                       |                          |                          |

| MTBF                                                  | 2102 years               | 2102 years               |

<sup>&</sup>lt;sup>11</sup> It is assumed that complete practical fault insertion tests can demonstrate the correctness of the failure effects assumed during the FMEDA.

<sup>&</sup>lt;sup>12</sup> Analysis 1 represents a worst-case analysis.

<sup>&</sup>lt;sup>13</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

Table 6: Summary for PT 4-...DC/AC-ST and BE – Failure rates 14

|                                                       | exida Profile 1        |                          |

|-------------------------------------------------------|------------------------|--------------------------|

|                                                       | Analysis 1 15          | Analysis 2 <sup>16</sup> |

| Failure category                                      | Failure rates (in FIT) | Failure rates (in FIT)   |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                      | 0                        |

| Fail Safe Undetected ( su)                            | 6.8                    | 6.8                      |

| Fail Dangerous Detected ( DD)                         | 0                      | 12.9                     |

| Fail Dangerous Undetected ( DU)                       | 15.6                   | 2.7                      |

|                                                       |                        |                          |

| No effect                                             | 51                     | 51                       |

| No part                                               | 0                      | 0                        |

|                                                       |                        | -                        |

| Total failure rate (interfering with safety function) | 22.4 FIT               | 22.4 FIT                 |

|                                                       |                        |                          |

| MTBF                                                  | 1562 years             | 1562 years               |

<sup>&</sup>lt;sup>14</sup> It is assumed that complete practical fault insertion tests can demonstrate the correctness of the failure effects assumed during the FMEDA.

<sup>&</sup>lt;sup>15</sup> Analysis 1 represents a worst-case analysis.

<sup>&</sup>lt;sup>16</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

Table 7: Summary for PT 4-...DC/AC-ST and BE+F – Failure rates <sup>17</sup>

|                                                       | <i>exida</i> F           | exida Profile 1          |  |

|-------------------------------------------------------|--------------------------|--------------------------|--|

|                                                       | Analysis 1 <sup>18</sup> | Analysis 2 <sup>19</sup> |  |

| Failure category                                      | Failure rates (in FIT)   | Failure rates (in FIT)   |  |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                        | 0                        |  |

| Fail Safe Undetected ( su)                            | 6.8                      | 6.8                      |  |

| Fail Dangerous Detected ( DD)                         | 0                        | 12.9                     |  |

| Fail Dangerous Undetected ( DU)                       | 15.6                     | 2.7                      |  |

|                                                       |                          | _                        |  |

| No effect                                             | 71                       | 71                       |  |

| No part                                               | 0                        | 0                        |  |

|                                                       |                          |                          |  |

| Total failure rate (interfering with safety function) | 22.4 FIT                 | 22.4 FIT                 |  |

|                                                       |                          | Ι                        |  |

| MTBF                                                  | 1226 years               | 1226 years               |  |

$<sup>^{17}</sup>$  It is assumed that complete practical fault insertion tests can demonstrate the correctness of the failure effects assumed during the FMEDA.

<sup>&</sup>lt;sup>18</sup> Analysis 1 represents a worst-case analysis.

<sup>&</sup>lt;sup>19</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

Table 8: Summary for PT 4-F-ST and BE – Failure rates 20

|                                                       | exida Profile 1          |                          |

|-------------------------------------------------------|--------------------------|--------------------------|

|                                                       | Analysis 1 <sup>21</sup> | Analysis 2 <sup>22</sup> |

| Failure category                                      | Failure rates (in FIT)   | Failure rates (in FIT)   |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                        | 0                        |

| Fail Safe Undetected ( <sub>SU</sub> )                | 2.5                      | 2.5                      |

| Fail Dangerous Detected ( DD)                         | 0                        | 1.4                      |

| Fail Dangerous Undetected ( DU)                       | 2.4                      | 1.0                      |

|                                                       |                          |                          |

| No effect                                             | 21                       | 21                       |

| No part                                               | 0                        | 0                        |

|                                                       |                          |                          |

| Total failure rate (interfering with safety function) | 4.9 FIT                  | 4.9 FIT                  |

| Luzze                                                 | 4400                     | 1400                     |

| MTBF                                                  | 4408 years               | 4408 years               |

$<sup>^{20}</sup>$  It is assumed that complete practical fault insertion tests can demonstrate the correctness of the failure effects assumed during the FMEDA.

<sup>&</sup>lt;sup>21</sup> Analysis 1 represents a worst-case analysis.

<sup>&</sup>lt;sup>22</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

Table 9: Summary for PT 3-...DC-ST and BE – Failure rates <sup>23</sup>

| <u>.</u>                                              |                          |                          |

|-------------------------------------------------------|--------------------------|--------------------------|

|                                                       | exida Profile 1          |                          |

|                                                       | Analysis 1 <sup>24</sup> | Analysis 2 <sup>25</sup> |

| Failure category                                      | Failure rates (in FIT)   | Failure rates (in FIT)   |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                        | 0                        |

| Fail Safe Undetected ( su)                            | 2.1                      | 2.1                      |

| Fail Dangerous Detected ( DD)                         | 0                        | 6.5                      |

| Fail Dangerous Undetected ( DU)                       | 8.2                      | 1.7                      |

|                                                       |                          |                          |

| No effect                                             | 25                       | 25                       |

| No part                                               | 0                        | 0                        |

|                                                       |                          |                          |

| Total failure rate (interfering with safety function) | 10.3 FIT                 | 10.3 FIT                 |

|                                                       |                          |                          |

| MTBF                                                  | 3271 years               | 3271 years               |

$<sup>^{23}</sup>$  It is assumed that complete practical fault insertion tests can demonstrate the correctness of the failure effects assumed during the FMEDA.

<sup>&</sup>lt;sup>24</sup> Analysis 1 represents a worst-case analysis.

<sup>&</sup>lt;sup>25</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

Table 10: Summary for PT 3-HF-...DC-ST / PT 3-PB-ST and BE – Failure rates <sup>26</sup>

|                                                       | exida Profile 1          |                          |

|-------------------------------------------------------|--------------------------|--------------------------|

|                                                       | Analysis 1 <sup>27</sup> | Analysis 2 <sup>28</sup> |

| Failure category                                      | Failure rates (in FIT)   | Failure rates (in FIT)   |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                        | 0                        |

| Fail Safe Undetected ( <sub>SU</sub> )                | 2.7                      | 2.7                      |

| Fail Dangerous Detected ( DD)                         | 0                        | 3.9                      |

| Fail Dangerous Undetected ( DU)                       | 8.4                      | 4.5                      |

|                                                       |                          |                          |

| No effect                                             | 30                       | 30                       |

| No part                                               | 0                        | 0                        |

|                                                       |                          |                          |

| Total failure rate (interfering with safety function) | 11.1 FIT                 | 11.1 FIT                 |

|                                                       |                          | •                        |

| MTBF                                                  | 2751 years               | 2751 years               |

$<sup>^{26}</sup>$  It is assumed that complete practical fault insertion tests can demonstrate the correctness of the failure effects assumed during the FMEDA.

<sup>&</sup>lt;sup>27</sup> Analysis 1 represents a worst-case analysis.

<sup>&</sup>lt;sup>28</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

Table 11: Summary for PT 3-HF-...DC-ST / PT 3-PB-ST and BE+F - Failure rates 29

|                                                       | exida Profile 1          |                          |

|-------------------------------------------------------|--------------------------|--------------------------|

|                                                       | Analysis 1 <sup>30</sup> | Analysis 2 <sup>31</sup> |

| Failure category                                      | Failure rates (in FIT)   | Failure rates (in FIT)   |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                        | 0                        |

| Fail Safe Undetected ( su)                            | 2.7                      | 2.7                      |

| Fail Dangerous Detected ( DD)                         | 0                        | 3.9                      |

| Fail Dangerous Undetected ( DU)                       | 8.4                      | 4.5                      |

|                                                       |                          |                          |

| No effect                                             | 50                       | 50                       |

| No part                                               | 0                        | 0                        |

|                                                       |                          |                          |

| Total failure rate (interfering with safety function) | 11.1 FIT                 | 11.1 FIT                 |

| _                                                     | ı                        | T                        |

| MTBF                                                  | 1856 years               | 1856 years               |

$<sup>^{29}</sup>$  It is assumed that complete practical fault insertion tests can demonstrate the correctness of the failure effects assumed during the FMEDA.

<sup>&</sup>lt;sup>30</sup> Analysis 1 represents a worst-case analysis.

<sup>&</sup>lt;sup>31</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

Table 12: Summary for PT 5-HF-...DC-ST and BE – Failure rates 32

|                                                       | exida Profile 1          |                          |

|-------------------------------------------------------|--------------------------|--------------------------|

|                                                       | Analysis 1 <sup>33</sup> | Analysis 2 <sup>34</sup> |

| Failure category                                      | Failure rates (in FIT)   | Failure rates (in FIT)   |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                        | 0                        |

| Fail Safe Undetected ( su)                            | 2.7                      | 2.7                      |

| Fail Dangerous Detected ( DD)                         | 0                        | 3.9                      |

| Fail Dangerous Undetected ( DU)                       | 8.4                      | 4.5                      |

|                                                       | _                        |                          |

| No effect                                             | 30                       | 30                       |

| No part                                               | 0                        | 0                        |

|                                                       |                          |                          |

| Total failure rate (interfering with safety function) | 11.1 FIT                 | 11.1 FIT                 |

|                                                       | 1                        | Т                        |

| MTBF                                                  | 2751 years               | 2751 years               |

Stephan Aschenbrenner

Phoenix Contact 14-09-007 R020.docx; March 30, 2016

<sup>32</sup> It is assumed that complete practical fault insertion tests can demonstrate the correctness of the failure effects assumed during the FMEDA.

<sup>&</sup>lt;sup>33</sup> Analysis 1 represents a worst-case analysis.

<sup>&</sup>lt;sup>34</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

Table 13: Summary for PT 5-HF-...DC-ST and BE+F – Failure rates 35

|                                                       |                          | -                        |

|-------------------------------------------------------|--------------------------|--------------------------|

|                                                       | exida Profile 1          |                          |

|                                                       | Analysis 1 <sup>36</sup> | Analysis 2 <sup>37</sup> |

| Failure category                                      | Failure rates (in FIT)   | Failure rates (in FIT)   |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                        | 0                        |

| Fail Safe Undetected ( su)                            | 2.7                      | 2.7                      |

| Fail Dangerous Detected ( DD)                         | 0                        | 3.9                      |

| Fail Dangerous Undetected ( DU)                       | 8.4                      | 4.5                      |

|                                                       |                          |                          |

| No effect                                             | 50                       | 50                       |

| No part                                               | 0                        | 0                        |

|                                                       |                          |                          |

| Total failure rate (interfering with safety function) | 11.1 FIT                 | 11.1 FIT                 |

|                                                       |                          |                          |

| MTBF                                                  | 1856 years               | 1856 years               |

$<sup>^{35}</sup>$  It is assumed that complete practical fault insertion tests can demonstrate the correctness of the failure effects assumed during the FMEDA.

<sup>&</sup>lt;sup>36</sup> Analysis 1 represents a worst-case analysis.

<sup>&</sup>lt;sup>37</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

Table 14: Summary for PT 2-TELE-ST and BE – Failure rates <sup>38</sup>

|                                                       | exida Profile 1          |                          |

|-------------------------------------------------------|--------------------------|--------------------------|

|                                                       | Analysis 1 <sup>39</sup> | Analysis 2 <sup>40</sup> |

| Failure category                                      | Failure rates (in FIT)   | Failure rates (in FIT)   |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                        | 0                        |

| Fail Safe Undetected ( su)                            | 2.7                      | 2.7                      |

| Fail Dangerous Detected ( DD)                         | 0                        | 4.3                      |

| Fail Dangerous Undetected ( DU)                       | 8.7                      | 4.4                      |

|                                                       |                          |                          |

| No effect                                             | 37                       | 37                       |

| No part                                               | 0                        | 0                        |

|                                                       |                          |                          |

| Total failure rate (interfering with safety function) | 11.4 FIT                 | 11.4 FIT                 |

|                                                       |                          |                          |

| MTBF                                                  | 2363 years               | 2363 years               |

The failure rates are valid for the useful life of the surge protective devices PLUGTRAB PT (see Appendix 2).

Phoenix Contact 14-09-007 R020.docx; March 30, 2016

$<sup>^{38}</sup>$  It is assumed that complete practical fault insertion tests can demonstrate the correctness of the failure effects assumed during the FMEDA.

<sup>&</sup>lt;sup>39</sup> Analysis 1 represents a worst-case analysis.

<sup>&</sup>lt;sup>40</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

## **Table of Contents**

| Ма  | nage | ement summary                                                                    | 2  |

|-----|------|----------------------------------------------------------------------------------|----|

| 1   | Pur  | pose and Scope                                                                   | 18 |

| 2   | Proj | ject management                                                                  | 19 |

|     | -    | exida                                                                            |    |

|     | 2.2  | Roles of the parties involved                                                    | 19 |

|     | 2.3  | Standards / Literature used                                                      | 19 |

|     | 2.4  | exida tools used                                                                 | 19 |

|     | 2.5  | Reference documents                                                              | 20 |

|     |      | 2.5.1 Documentation provided by the customer                                     | 20 |

|     |      | 2.5.2 Documentation generated by <i>exida</i>                                    | 20 |

| 3   | Des  | scription of the analyzed devices                                                | 21 |

| 4   | Fail | ure Modes, Effects, and Diagnostic Analysis                                      | 25 |

|     |      | Description of the failure categories                                            |    |

|     | 4.2  | Methodology – FMEDA, Failure rates                                               | 26 |

|     |      | 4.2.1 FMEDA                                                                      | 26 |

|     |      | 4.2.2 Failure rates                                                              | 26 |

|     | 4.3  | Assumptions                                                                      | 27 |

|     | 4.4  | Results                                                                          |    |

|     |      | 4.4.1 PT 2x2DC/AC-ST and BE                                                      |    |

|     |      | 4.4.2 PT 2x2DC/AC-ST and BE+F                                                    | 29 |

|     |      | 4.4.3 PT 1x2DC/AC-ST and BE                                                      |    |

|     |      | 4.4.4 PT 1x2DC/AC-ST and BE+F                                                    |    |

|     |      | 4.4.5 PT 4DC/AC-ST and BE                                                        |    |

|     |      | 4.4.6 PT 4DC/AC-ST and BE+F                                                      |    |

|     |      | 4.4.7 PT 4-F-ST and BE                                                           |    |

|     |      | 4.4.8 PT 3DC-ST and BE                                                           |    |

|     |      | 4.4.9 PT 3-HFDC-ST / PT 3-PB-ST and BE                                           |    |

|     |      | 4.4.10 PT 3-HFDC-ST / PT 3-PB-ST and BE+F                                        |    |

|     |      | 4.4.11 PT 5-HFDC-ST and BE                                                       |    |

|     |      | 4.4.12 PT 5-HFDC-ST and BE+F                                                     |    |

|     |      | 4.4.13 PT 2-TELE-ST and BE                                                       |    |

| 5   |      | ng the FMEDA results                                                             |    |

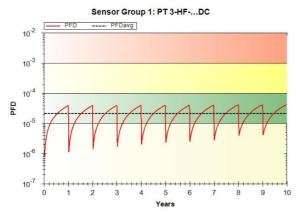

|     | 5.1  | Example PFD <sub>AVG</sub> / PFH calculation                                     | 41 |

| 6   | Terr | ms and Definitions                                                               | 42 |

| 7   | Stat | tus of the document                                                              | 43 |

|     | 7.1  | Liability                                                                        | 43 |

|     |      | Releases                                                                         |    |

|     | 7.3  | Release Signatures                                                               | 43 |

| App | pend | dix 1: Possibilities to reveal dangerous undetected faults during the proof test | 44 |

|     | App  | pendix 1.1: Proof test to detect dangerous undetected faults                     | 44 |

|     |      |                                                                                  |    |

| Appendix 2: Impact of lifetime of critical components on the failure rate | .45 |

|---------------------------------------------------------------------------|-----|

| Appendix 3: exida Environmental Profiles                                  | 46  |

## 1 Purpose and Scope

This document shall describe the results of hardware assessment according to IEC 61508 carried out on the surge protective devices PLUGTRAB PT in the versions listed in the drawings referenced in section 2.5.1. Table 1 gives an overview of the different configurations that belong to the considered surge protective devices PLUGTRAB PT.

The FMEDA builds the basis for an evaluation whether a sensor or final element subsystem, including the surge protective devices PLUGTRAB PT meets the average Probability of Failure on Demand ( $PFD_{AVG}$ ) / Probability of dangerous Failure per Hour (PFH) requirements and if applicable the architectural constraints / minimum hardware fault tolerance requirements per IEC 61508 / IEC 61511. It **does not** consider any calculations necessary for proving intrinsic safety or the correct functioning of the surge protective devices.

© exida.com GmbH

## 2 Project management

#### 2.1 exida

exida is one of the world's leading accredited Certification Bodies and knowledge companies specializing in automation system safety and availability with over 300 years of cumulative experience in functional safety. Founded by several of the world's top reliability and safety experts from assessment organizations and manufacturers, exida is a global company with offices around the world. exida offers training, coaching, project oriented system consulting services, safety lifecycle engineering tools, detailed product assurance, cyber-security and functional safety certification, and a collection of on-line safety and reliability resources. exida maintains a comprehensive failure rate and failure mode database on process equipment.

## 2.2 Roles of the parties involved

PHOENIX CONTACT GmbH & Co. KG Manufacturer of the surge protective devices PLUGTRAB PT.

exida Performed the hardware assessment.

PHOENIX CONTACT GmbH & Co. KG contracted *exida* in February 2016 with the extension and update of this report.

#### 2.3 Standards / Literature used

The services delivered by *exida* were performed based on the following standards / literature.

| [N1] | IEC 61508-2:2010                                                | Functional Safety of<br>Electrical/Electronic/Programmable Electronic<br>Safety-Related Systems          |

|------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| [N2] | Electrical Component Reliability<br>Handbook, 3rd Edition, 2012 | exida LLC, Electrical Component Reliability<br>Handbook, Third Edition, 2012, ISBN 978-1-<br>934977-04-0 |

#### 2.4 exida tools used

© exida.com GmbH

| [T1] | SILcal V8.0.12        | FMEDA Tool            |

|------|-----------------------|-----------------------|

| [T2] | exSILentia V3.3.0.906 | SIL Verification Tool |

#### 2.5 Reference documents

### 2.5.1 Documentation provided by the customer

| [D1] | SIL- FMEDA-Bericht PT2x2,    | Safety considerations for PLUGTRAB PT including |

|------|------------------------------|-------------------------------------------------|

|      | PT1x2, PT4, PT3_R02_V01.docx | parts lists and circuit diagrams; 29.03.2016    |

The list above only means that the referenced documents were provided as basis for the FMEDA but it does not mean that *exida* checked the correctness and completeness of these documents.

### 2.5.2 Documentation generated by exida

| [R1]  | FMEDA_V8_PT 1x2DC_AC_V1R0.efm of 09.09.2014          |

|-------|------------------------------------------------------|

| [R2]  | FMEDA_V8_PT 1x2DC_AC_w_ED_V1R0.efm of 29.09.2014     |

| [R3]  | FMEDA_V8_PT 1x2DC_AC+F_V1R0.efm of 12.09.2014        |

| [R4]  | FMEDA_V8_PT 1x2DC_AC+F_w_ED_V1R0.efm of 29.09.2014   |

| [R5]  | FMEDA_V8_PT 2x2DC_AC_V1R0.efm of 09.09.2014          |

| [R6]  | FMEDA_V8_PT 2x2DC_AC_w_ED_V1R0.efm of 29.09.2014     |

| [R7]  | FMEDA_V8_PT 2x2DC_AC+F_V1R0.efm of 12.09.2014        |

| [R8]  | FMEDA_V8_PT 2x2DC_AC+F_w_ED_V1R0.efm of 29.09.2014   |

| [R9]  | FMEDA_V8_PT 3DC_V1R1.efm of 15.09.2014               |

| [R10] | FMEDA_V8_PT 3DC_w_ED_V1R1.efm of 29.09.2014          |

| [R11] | FMEDA_V8_PT 4DC_V1R0.efm of 09.09.2014               |

| [R12] | FMEDA_V8_PT 4DC_w_ED_V1R0.efm of 29.09.2014          |

| [R13] | FMEDA_V8_PT 4DC+F_V1R1.efm of 15.09.2014             |

| [R14] | FMEDA_V8_PT 4DC+F_w_ED_V1R1.efm of 29.09.2014        |

| [R15] | FMEDA_V8_PT 4+F_V1R0.efm of 09.09.2014               |

| [R16] | FMEDA_V8_PT 4+F_w_ED_V1R0.efm of 29.09.2014          |

| [R17] | FMEDA_V8_PT 3HF_PT 3PB_V1R1.efm of 24.03.2016        |

| [R18] | FMEDA_V8_PT 3HF_PT 3PB_w_ED_V1R1.efm of 24.03.2016   |

| [R19] | FMEDA_V8_PT 3HF_PT 3PB+F_V1R1.efm of 24.03.2016      |

| [R20] | FMEDA_V8_PT 3HF_PT 3PB+F_w_ED_V1R1.efm of 24.03.2016 |

| [R21] | FMEDA_V8_PT 5HF_V1R1.efm of 24.03.2016               |

| [R22] | FMEDA_V8_PT 5HF_w_ED_V1R1.efm of 24.03.2016          |

| [R23] | FMEDA_V8_PT 5HF+F_V1R1.efm of 24.03.2016             |

| [R24] | FMEDA_V8_PT 5HF+F_w_ED_V1R1.efm of 24.03.2016        |

| [R25] | FMEDA_V8_PT2-TELE_V1R1.efm of 24.03.2016             |

| [R26] | FMEDA_V8_PT2-TELE_w_ED_V1R1.efm of 24.03.2016        |

Phoenix Contact 14-09-007 R020.docx; March 30, 2016

Page 20 of 46

# 3 Description of the analyzed devices

The FMEDA of the surge protective devices PLUGTRAB PT has been carried out on the parts indicated in Figure 1 to Figure 8.

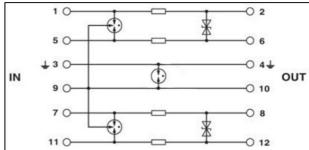

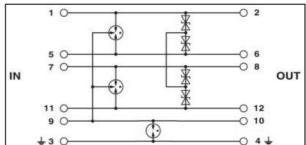

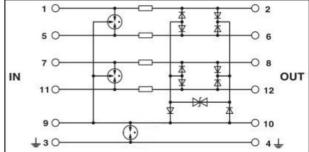

PT 2x2-...DC/AC is a surge voltage protection device for two separate floating signal circuits. A fine protection element guarantees a low voltage threshold in conjunction with fast response between the corresponding cores. The high surge arresting capacity is achieved by using gas-filled surge voltage arresters from each wire to the common reference potential. PT 2x2...-ST is installed together with the PT 2x2-BE or the PT 2x2+F-BE base element.

Figure 1: Block diagram of the surge protective device PT 2x2-...DC/AC

PT 1x2-...DC/AC is a surge voltage protection device for one floating signal circuit. A fine protection element guarantees a low voltage threshold in conjunction with fast response between the corresponding cores. The high surge arresting capacity is achieved by using gas-filled surge voltage arresters from each wire to the common reference potential. PT 1x2...-ST is installed together with the PT 1x2-BE or the PT 1x2+F-BE base element.

Figure 2: Block diagram of the surge protective device PT 1x2-...DC/AC

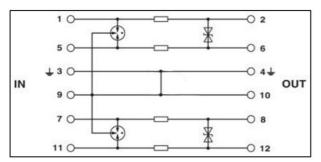

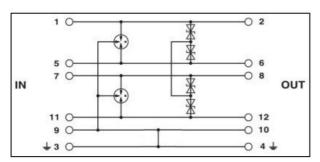

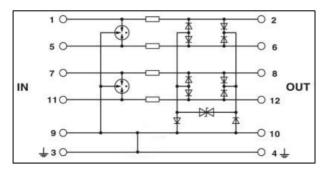

PT 4-...DC/AC is a surge voltage protection device for two, three or four-conductor signal circuits. By arranging suppressor diodes between all the signal wires, fine protection between them is achieved together with fast response. The use of gas-filled surge voltage arresters from each wire to the common reference potential guarantees the high surge arresting capacity. PT 4...-ST is installed together with the PT 4-BE or the PT 4+F-BE base element.

Figure 3: Block diagram of the surge protective device PT 4-...DC/AC

Phoenix Contact 14-09-007 R020.docx; March 30, 2016

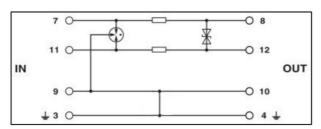

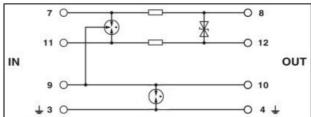

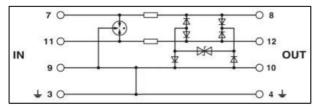

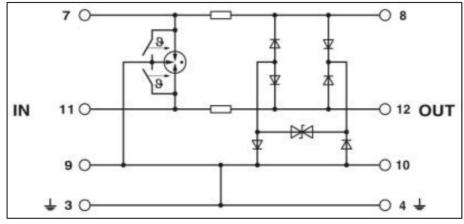

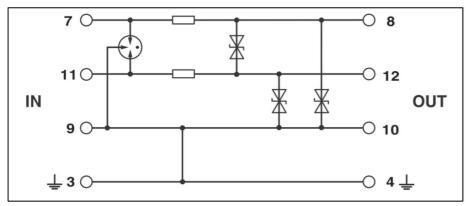

PT 3-HF-...DC and PT 3-PB are surge voltage protection devices for normal mode voltage coarse and fine protection for two floating signal wires and ground in IT, common mode voltage coarse protection to ground/earth. PT 3-HF...-ST and PT 3-PB-ST are installed together with the PT 1x2-BE or the PT 1x2+F-BE base element.

Figure 4: Block diagram of the surge protective device PT 3-HF-...DC and PT 3-PB

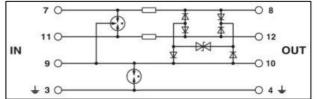

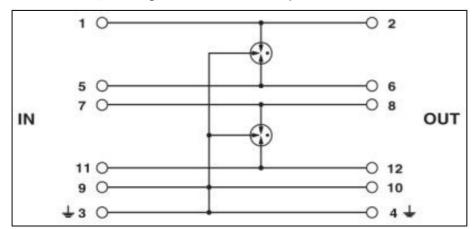

PT 5-HF-...DC is a surge voltage protection device for normal mode voltage coarse and fine protection for four floating signal wires and ground in IT, common mode voltage coarse protection to ground/earth.PT 5-HF...-ST is installed together with the PT 2x2-BE or the PT 2x2+F-BE base element.

Figure 5: Block diagram of the surge protective device PT 5-HF-...DC

PT 2-TELE is a surge voltage protection device, consisting of plug and base element, for protecting a double wire from analog and digital telecommunications interfaces (VDSL up to 50 Mbps). PT 2-TELE-ST is installed together with the PT 1x2-BE base element.

Figure 6: Block diagram of the surge protective device PT 2-TELE

© exida.com GmbH

PT 4-F is a surge voltage protection device for four signal wires with common reference potential. The high surge arresting capacity is achieved by using gas-filled surge voltage arresters from each wire to the common reference potential. PT 4-F-ST is installed together with the PT 4-BE base element, which ground the reference potential.

Figure 7: Block diagram of the surge protective device PT 4-F

PT 3-...DC is a surge voltage protection device for two signal wires with common reference potential. Three fine protection elements guarantee a low voltage threshold in conjunction with fast response between the corresponding wires. The high surge arresting capacity is achieved by using gas-filled surge voltage arresters from each wire to the common reference potential. PT 3...-ST is installed together with the PT 3-1R2-BE base element, which ground the reference potential.

Figure 8: Block diagram of the surge protective device PT 3-...DC

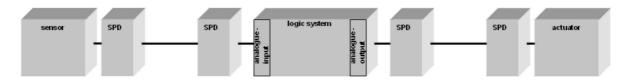

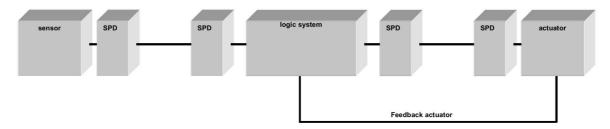

The following two figures Figure 9 and Figure 10 show how the surge protective devices (SPD) can be connected to other devices. All considered surge protective devices can be used with analog or binary devices.

Figure 9: Connection with analog devices

Figure 10: Connection with binary devices

Figure 11 shows how faults of the surge protective devices on the actuator side can be detected. On the sensor side faults can be detected by the safety PLC via an out of range check as the input signal will be outside the allowed range of 4-20mA or 2-10V in case of line short circuits and short circuits to GND.

Figure 11: Connection for fault detection

© exida.com GmbH Stephan Aschenbrenner

## 4 Failure Modes, Effects, and Diagnostic Analysis

The Failure Modes, Effects, and Diagnostic Analysis was done together with PHOENIX CONTACT GmbH & Co. KG and is documented in [R1] to [R26]. Failures have been classified according to the following failure categories.

#### 4.1 Description of the failure categories

In order to judge the failure behavior of the surge protective devices PLUGTRAB PT, the following definitions for the failure of the product were considered.

Fail-Safe State The fail-safe state is defined as the output being de-energized or

reaching the user defined threshold value or the predefined alarm

state.

Safe A safe failure (S) is defined as a failure that plays a part in implementing

the safety function that:

a) results in the spurious operation of the safety function to put the EUC (or part thereof) into a safe state or maintain a safe state; or,

b) increases the probability of the spurious operation of the safety function to put the EUC (or part thereof) into a safe state or maintain

a safe state.

Dangerous A dangerous failure (D) is defined as a failure that plays a part in

implementing the safety function that:

a) prevents a safety function from operating when required (demand mode) or causes a safety function to fail (continuous mode) such that the EUC is put into a hazardous or potentially hazardous state;

or,

b) decreases the probability that the safety function operates correctly

when required.

Dangerous Undetected Failure that is dangerous and that is not being diagnosed by internal or

external diagnostics (DU).

Dangerous Detected Failure that is dangerous but is detected by external diagnostics (DD).

No effect Failure mode of a component that plays a part in implementing the

safety function but is neither a safe failure nor a dangerous failure.

No part Component that plays no part in implementing the safety function but

is part of the circuit diagram and is listed for completeness.

### 4.2 Methodology – FMEDA, Failure rates

#### 4.2.1 FMEDA

A Failure Modes and Effects Analysis (FMEA) is a systematic way to identify and evaluate the effects of different component failure modes, to determine what could eliminate or reduce the chance of failure, and to document the system in consideration.

A FMEDA (Failure Modes, Effects, and Diagnostic Analysis) is a FMEA extension. It combines standard FMEA techniques with extension to identify online diagnostics techniques and the failure modes relevant to safety instrumented system design. It is a technique recommended to generate failure rates for each important category (safe detected, safe undetected, dangerous detected, dangerous undetected, fail high, fail low) in the safety models. The format for the FMEDA is an extension of the standard FMEA format from MIL STD 1629A, Failure Modes and Effects Analysis.

#### 4.2.2 Failure rates

The failure rate data used by *exida* in this FMEDA is from the Electrical Component Reliability Handbook ([N2]) which was derived using over ten billion unit operational hours of field failure data from multiple sources and failure data from various databases. The rates were chosen in a way that is appropriate for safety integrity level verification calculations. The rates were chosen to match operating stress conditions typical of an industrial field environment similar to *exida* Profile 1. It is expected that the actual number of field failures due to random events will be less than the number predicted by these failure rates.

For hardware assessment according to IEC 61508 only random equipment failures are of interest. It is assumed that the equipment has been properly selected for the application and is adequately commissioned such that early life failures (infant mortality) may be excluded from the analysis.

Failures caused by external events however should be considered as random failures. Examples of such failures are loss of power or physical abuse.

The assumption is also made that the equipment is maintained per the requirements of IEC 61508 or IEC 61511 and therefore a preventative maintenance program is in place to replace equipment before the end of its "useful life".

The user of these numbers is responsible for determining their applicability to any particular environment. Accurate plant specific data may be used for this purpose. If a user has data collected from a good proof test reporting system such as exida SILStat<sup>TM</sup> that indicates higher failure rates, the higher numbers shall be used. Some industrial plant sites have high levels of stress. Under those conditions the failure rate data is adjusted to a higher value to account for the specific conditions of the plant.

#### 4.3 Assumptions

The following assumptions have been made during the Failure Modes, Effects, and Diagnostic Analysis of the surge protective devices PLUGTRAB PT.

- ∞ Failure rates are constant, wear out mechanisms are not included.

- ∞ Propagation of failures is not relevant.

- $\infty$  The device is installed per manufacturer's instructions.

- $\infty$  The device is used within its specified limits.

- Sufficient tests are performed prior to shipment to verify the absence of vendor and/or manufacturing defects that prevent proper operation of specified functionality to product specifications or cause operation different from the design analyzed.

- $\infty$  For safety applications only the described configurations are considered.

- $\infty$  In case of multiple channel devices only one channel is part of the considered safety function.

- ∞ External power supply failure rates are not included.

- ∞ The mean time to restoration (MTTR) after a safe failure is 24 hours.

#### 4.4 Results

For the calculation the following has to be noted:

total consists of the sum of all component failure rates. This means:

$$_{total}$$

=  $_{SD}$  +  $_{SU}$  +  $_{DD}$  +  $_{DU}$

MTBF = MTTF + MTTR =  $(1 / (_{total}$  +  $_{no \, effect}$  +  $_{no \, part}))$  + 24 h

### 4.4.1 PT 2x2-...DC/AC-ST and BE

The FMEDA carried out on the surge protective devices PT 2x2-...DC/AC-ST and BE leads under the assumptions described in section 4.3 and the definitions given in section 4.1 to the following failure rates:

|                                                       | exida Profile 1          |                          |

|-------------------------------------------------------|--------------------------|--------------------------|

|                                                       | Analysis 1 <sup>41</sup> | Analysis 2 <sup>42</sup> |

| Failure category                                      | Failure rates (in FIT)   | Failure rates (in FIT)   |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                        | 0                        |

| Fail Safe Undetected ( <sub>SU</sub> )                | 2.7                      | 2.7                      |

| Fail Dangerous Detected ( DD)                         | 0                        | 3.9                      |

| Fail Dangerous Undetected ( DU)                       | 5.8                      | 1.9                      |

|                                                       |                          |                          |

| No effect                                             | 26                       | 26                       |

| No part                                               | 0                        | 0                        |

|                                                       |                          |                          |

| Total failure rate (interfering with safety function) | 8.5 FIT                  | 8.5 FIT                  |

|                                                       |                          |                          |

| MTBF                                                  | 3328 years               | 3328 years               |

See the product details here

<sup>&</sup>lt;sup>42</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

© exida.com GmbH

<sup>&</sup>lt;sup>41</sup> Analysis 1 represents a worst-case analysis.

## 4.4.2 PT 2x2-...DC/AC-ST and BE+F

The FMEDA carried out on the surge protective devices PT 2x2-...DC/AC-ST and BE+F leads under the assumptions described in section 4.3 and the definitions given in section 4.1 to the following failure rates:

|                                                       | exida Profile 1          |                          |

|-------------------------------------------------------|--------------------------|--------------------------|

|                                                       | Analysis 1 <sup>43</sup> | Analysis 2 <sup>44</sup> |

| Failure category                                      | Failure rates (in FIT)   | Failure rates (in FIT)   |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                        | 0                        |

| Fail Safe Undetected ( su)                            | 2.7                      | 2.7                      |

| Fail Dangerous Detected ( DD)                         | 0                        | 3.9                      |

| Fail Dangerous Undetected ( DU)                       | 5.8                      | 1.9                      |

|                                                       |                          |                          |

| No effect                                             | 46                       | 46                       |

| No part                                               | 0                        | 0                        |

|                                                       |                          |                          |

| Total failure rate (interfering with safety function) | 8.5 FIT                  | 8.5 FIT                  |

| T                                                     | T                        | T                        |

| MTBF                                                  | 2102 years               | 2102 years               |

<sup>&</sup>lt;sup>44</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

© exida.com GmbH

<sup>&</sup>lt;sup>43</sup> Analysis 1 represents a worst-case analysis.

### 4.4.3 PT 1x2-...DC/AC-ST and BE

The FMEDA carried out on the surge protective devices PT 1x2-...DC/AC-ST and BE leads under the assumptions described in section 4.3 and the definitions given in section 4.1 to the following failure rates:

|                                                       | exida Profile 1          |                          |

|-------------------------------------------------------|--------------------------|--------------------------|

|                                                       | Analysis 1 <sup>45</sup> | Analysis 2 <sup>46</sup> |

| Failure category                                      | Failure rates (in FIT)   | Failure rates (in FIT)   |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                        | 0                        |

| Fail Safe Undetected ( <sub>SU</sub> )                | 2.7                      | 2.7                      |

| Fail Dangerous Detected ( DD)                         | 0                        | 3.9                      |

| Fail Dangerous Undetected ( DU)                       | 5.8                      | 1.9                      |

|                                                       |                          |                          |

| No effect                                             | 26                       | 26                       |

| No part                                               | 0                        | 0                        |

|                                                       |                          |                          |

| Total failure rate (interfering with safety function) | 8.5 FIT                  | 8.5 FIT                  |

|                                                       |                          |                          |

| MTBF                                                  | 3328 years               | 3328 years               |

<sup>&</sup>lt;sup>46</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

© exida.com GmbH

<sup>&</sup>lt;sup>45</sup> Analysis 1 represents a worst-case analysis.

#### 4.4.4 PT 1x2-...DC/AC-ST and BE+F

The FMEDA carried out on the surge protective devices PT 1x2-...DC/AC-ST and BE+F leads under the assumptions described in section 4.3 and the definitions given in section 4.1 to the following failure rates:

|                                                       | exida Profile 1                                   |                        |

|-------------------------------------------------------|---------------------------------------------------|------------------------|

|                                                       | Analysis 1 <sup>47</sup> Analysis 2 <sup>48</sup> |                        |

| Failure category                                      | Failure rates (in FIT)                            | Failure rates (in FIT) |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                                                 | 0                      |

| Fail Safe Undetected ( su)                            | 2.7                                               | 2.7                    |

| Fail Dangerous Detected ( DD)                         | 0                                                 | 3.9                    |

| Fail Dangerous Undetected ( DU)                       | 5.8                                               | 1.9                    |

|                                                       |                                                   |                        |

| No effect                                             | 46                                                | 46                     |

| No part                                               | 0                                                 | 0                      |

|                                                       |                                                   |                        |

| Total failure rate (interfering with safety function) | 8.5 FIT                                           | 8.5 FIT                |

|                                                       |                                                   |                        |

| MTBF                                                  | 2102 years                                        | 2102 years             |

<sup>&</sup>lt;sup>48</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

© exida.com GmbH

<sup>&</sup>lt;sup>47</sup> Analysis 1 represents a worst-case analysis.

### 4.4.5 PT 4-...DC/AC-ST and BE

The FMEDA carried out on the surge protective devices PT 4-...DC/AC-ST and BE leads under the assumptions described in section 4.3 and the definitions given in section 4.1 to the following failure rates:

|                                                       | exida Profile 1                                   |                        |

|-------------------------------------------------------|---------------------------------------------------|------------------------|

|                                                       | Analysis 1 <sup>49</sup> Analysis 2 <sup>50</sup> |                        |

| Failure category                                      | Failure rates (in FIT)                            | Failure rates (in FIT) |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                                                 | 0                      |

| Fail Safe Undetected ( <sub>SU</sub> )                | 6.8                                               | 6.8                    |

| Fail Dangerous Detected ( DD)                         | 0                                                 | 12.9                   |

| Fail Dangerous Undetected ( DU)                       | 15.6                                              | 2.7                    |

|                                                       |                                                   |                        |

| No effect                                             | 51                                                | 51                     |

| No part                                               | 0                                                 | 0                      |

|                                                       |                                                   |                        |

| Total failure rate (interfering with safety function) | 22.4 FIT                                          | 22.4 FIT               |

|                                                       | T                                                 | <u> </u>               |

| MTBF                                                  | 1562 years                                        | 1562 years             |

$<sup>^{50}</sup>$  Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

© exida.com GmbH

<sup>&</sup>lt;sup>49</sup> Analysis 1 represents a worst-case analysis.

### 4.4.6 PT 4-...DC/AC-ST and BE+F

The FMEDA carried out on the surge protective devices PT 4-...DC/AC-ST and BE+F leads under the assumptions described in section 4.3 and the definitions given in section 4.1 to the following failure rates:

|                                                       | exida F                  | exida Profile 1          |  |

|-------------------------------------------------------|--------------------------|--------------------------|--|

|                                                       | Analysis 1 <sup>51</sup> | Analysis 2 <sup>52</sup> |  |

| Failure category                                      | Failure rates (in FIT)   | Failure rates (in FIT)   |  |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                        | 0                        |  |

| Fail Safe Undetected ( su)                            | 6.8                      | 6.8                      |  |

| Fail Dangerous Detected ( DD)                         | 0                        | 12.9                     |  |

| Fail Dangerous Undetected ( DU)                       | 15.6                     | 2.7                      |  |

|                                                       |                          |                          |  |

| No effect                                             | 71                       | 71                       |  |

| No part                                               | 0                        | 0                        |  |

|                                                       |                          |                          |  |

| Total failure rate (interfering with safety function) | 22.4 FIT                 | 22.4 FIT                 |  |

|                                                       |                          | ı                        |  |

| MTBF                                                  | 1226 years               | 1226 years               |  |

<sup>&</sup>lt;sup>52</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

© exida.com GmbH

<sup>&</sup>lt;sup>51</sup> Analysis 1 represents a worst-case analysis.

#### 4.4.7 PT 4-F-ST and BE

The FMEDA carried out on the surge protective devices PT 4-F-ST and BE leads under the assumptions described in section 4.3 and the definitions given in section 4.1 to the following failure rates:

|                                                       | exida Profile 1                                   |                        |

|-------------------------------------------------------|---------------------------------------------------|------------------------|

|                                                       | Analysis 1 <sup>53</sup> Analysis 2 <sup>54</sup> |                        |

| Failure category                                      | Failure rates (in FIT)                            | Failure rates (in FIT) |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                                                 | 0                      |

| Fail Safe Undetected ( su)                            | 2.5                                               | 2.5                    |

| Fail Dangerous Detected ( DD)                         | 0                                                 | 1.4                    |

| Fail Dangerous Undetected ( DU)                       | 2.4                                               | 1.0                    |

|                                                       |                                                   |                        |

| No effect                                             | 21                                                | 21                     |

| No part                                               | 0                                                 | 0                      |

|                                                       |                                                   |                        |

| Total failure rate (interfering with safety function) | 4.9 FIT                                           | 4.9 FIT                |

|                                                       | T                                                 | Γ                      |

| MTBF                                                  | 4408 years                                        | 4408 years             |

<sup>&</sup>lt;sup>54</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

© exida.com GmbH

<sup>&</sup>lt;sup>53</sup> Analysis 1 represents a worst-case analysis.

#### 4.4.8 PT 3-...DC-ST and BE

The FMEDA carried out on the surge protective devices PT 3-...DC-ST and BE leads under the assumptions described in section 4.3 and the definitions given in section 4.1 to the following failure rates:

|                                                       | exida F                  | exida Profile 1          |  |

|-------------------------------------------------------|--------------------------|--------------------------|--|

|                                                       | Analysis 1 <sup>55</sup> | Analysis 2 <sup>56</sup> |  |

| Failure category                                      | Failure rates (in FIT)   | Failure rates (in FIT)   |  |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                        | 0                        |  |

| Fail Safe Undetected ( <sub>SU</sub> )                | 2.1                      | 2.1                      |  |

| Fail Dangerous Detected ( DD)                         | 0                        | 6.5                      |  |

| Fail Dangerous Undetected ( DU)                       | 8.2                      | 1.7                      |  |

|                                                       |                          |                          |  |

| No effect                                             | 25                       | 25                       |  |

| No part                                               | 0                        | 0                        |  |

|                                                       |                          |                          |  |

| Total failure rate (interfering with safety function) | 10.3 FIT                 | 10.3 FIT                 |  |

|                                                       |                          | Ι                        |  |

| MTBF                                                  | 3271 years               | 3271 years               |  |

<sup>&</sup>lt;sup>56</sup> Analysis 2 represents an analysis with the assumption that line short circuits and short circuits to GND are detectable or do not have an effect.

© exida.com GmbH

<sup>&</sup>lt;sup>55</sup> Analysis 1 represents a worst-case analysis.

#### 4.4.9 PT 3-HF-...DC-ST / PT 3-PB-ST and BE

The FMEDA carried out on the surge protective devices PT 3-HF-...DC-ST / PT 3-PB-ST and BE leads under the assumptions described in section 4.3 and the definitions given in section 4.1 to the following failure rates:

|                                                       | exida Profile 1                                   |                        |

|-------------------------------------------------------|---------------------------------------------------|------------------------|

|                                                       | Analysis 1 <sup>57</sup> Analysis 2 <sup>58</sup> |                        |

| Failure category                                      | Failure rates (in FIT)                            | Failure rates (in FIT) |

| Fail Safe Detected ( <sub>SD</sub> )                  | 0                                                 | 0                      |

| Fail Safe Undetected ( <sub>SU</sub> )                | 2.7                                               | 2.7                    |

| Fail Dangerous Detected ( DD)                         | 0                                                 | 3.9                    |

| Fail Dangerous Undetected ( DU)                       | 8.4 4.                                            |                        |

|                                                       |                                                   |                        |

| No effect                                             | 30                                                | 30                     |

| No part                                               | 0                                                 | 0                      |

|                                                       |                                                   |                        |

| Total failure rate (interfering with safety function) | 11.1 FIT                                          | 11.1 FIT               |